## W5100 Datasheet

Version 1.2.3

© 2010 WIZnet Co., Inc. All Rights Reserved. For more information, visit our website at <a href="http://www.wiznet.co.kr">http://www.wiznet.co.kr</a>

## **Document History Information**

| Version    | Date          | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ver. 1.0.0 | Dec. 21, 2006 | Released with W5100 Launching                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ver. 1.0.1 | Jan. 10, 2006 | LB bit in Mode register is not used .<br>W5100 is used only in Big-endian ordering.                                                                                                                                                                                                                                                                                                                                                                                          |

| Ver. 1.1.1 | Jun. 19, 2007 | Modified the OPMODE2-0 signals descriptions (P. 10) Modified the TEST_MODE3-0 signals description (P.11) Modified the Clock signals description (P.12) Modified the LINKLED signal description (P.12) Modified the explanation of RECV_INT in Sn_IR register (P. 27) Replaced the reset value of Sn_DHAR register (0x00 to 0xFF, P. 30) Modifted the explanation of Sn_DIPR, Sn_DPORT register (P. 31) Replaced the reset value of Sn_MSS register (0xFFFF to 0x0000, P. 31) |

| Ver. 1.1.2 | Sep. 28, 2007 | Modified the Operating temperature (P. 63)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

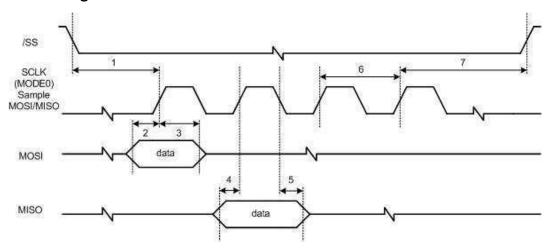

| Ver. 1.1.3 | Oct. 8, 2007  | Changed the typing error "MISO signal" (P. 10) Modified the SPI Timing diagram and description (P. 66)                                                                                                                                                                                                                                                                                                                                                                       |

| Ver. 1.1.4 | Oct. 18, 2007 | Modified the diagram (P. 40)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ver. 1.1.5 | Nov. 1, 2007  | Modified the Crystal Characteristics value (P. 67)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ver. 1.1.6 | Jan. 30, 2008 | Modified the SEN signals description (P.10) Changed the typing error "SCLK" (P. 66)                                                                                                                                                                                                                                                                                                                                                                                          |

| Ver. 1.1.7 | Feb. 12, 2009 | Changed the typing error "memory test mode" (P. 19) Changed the description & type of clock signals (P. 12) Modified DC characteristic value(p. 63)                                                                                                                                                                                                                                                                                                                          |

| Ver. 1.2   | Feb. 11, 2010 | Add the power supply signal schematic (P. 12)                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ver. 1.2.1 | Jun. 10, 2010 | Add Sn_TX_WR value changing condition                                                                                                                                                                                                                                                                                                                                                                                                                                        |

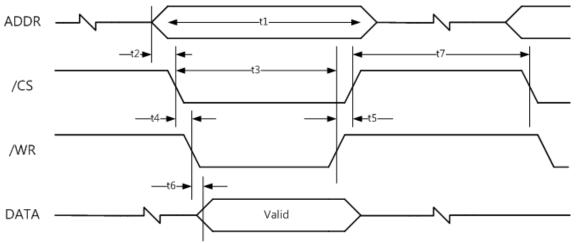

| Ver. 1.2.2 | Jun. 28, 2010 | Modify RD/WR timing diagram (P. 65, 66)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ver. 1.2.3 | Feb. 16, 2011 | Change the value of SOCK_ARP(0x01) state (P.31)                                                                                                                                                                                                                                                                                                                                                                                                                              |

### WIZnet's online Technical Support

If you have something to ask about WIZnet Products, write down your question on <u>Q&A Board</u> of 'Support' menu in WIZnet website (<u>www.wiznet.co.kr</u>). WIZnet Engineer will give an answer as soon as possible.

#### W5100 Datasheet

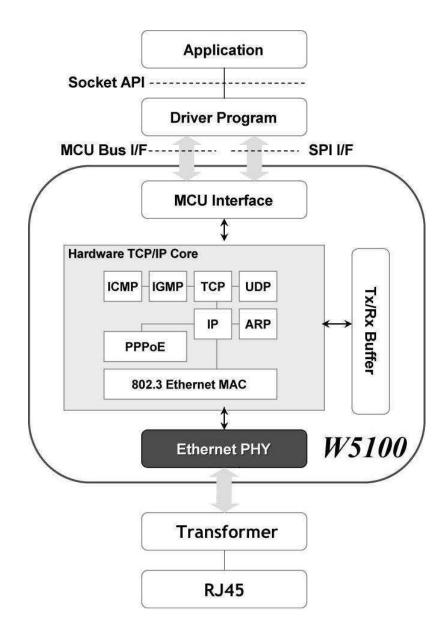

The W5100 is a full-featured, single-chip <u>Internet-enabled</u> 10/100 Ethernet controller designed for embedded applications where ease of integration, stability, performance, area and system cost control are required. The W5100 has been designed to facilitate easy implementation of Internet connectivity without OS. The W5100 is IEEE 802.3 10BASE-T and 802.3u 100BASE-TX compliant.

The W5100 includes fully hardwired, <u>market-proven TCP/IP stack</u> and integrated Ethernet MAC & PHY. Hardwired TCP/IP stack supports TCP, UDP, IPv4, ICMP, ARP, IGMP and PPPoE which has been proven in various applications for several years. 16Kbytes internal buffer is included for data transmission. No need of consideration for handling Ethernet Controller, but simple socket programming is required.

For easy integration, three different interfaces like memory access way, called direct, indirect bus and SPI, are supported on the MCU side.

### **Target Applications**

The W5100 is well suited for many embedded applications, including:

- Home Network Devices: Set-Top Boxes, PVRs, Digital Media Adapters

- Serial-to-Ethernet: Access Controls, LED displays, Wireless AP relays, etc.

- Parallel-to-Ethernet: POS / Mini Printers, Copiers

- USB-to-Ethernet: Storage Devices, Network Printers

- GPIO-to-Ethernet: Home Network Sensors

- Security Systems: DVRs, Network Cameras, Kiosks

- Factory and Building Automations

- Medical Monitoring Equipments

- Embedded Servers

#### **Features**

- Support Hardwired TCP/IP Protocols: TCP, UDP, ICMP, IPv4 ARP, IGMP, PPPoE, Ethernet

- 10BaseT/100BaseTX Ethernet PHY embedded

- Support Auto Negotiation (Full-duplex and half duplex)

- Support Auto MDI/MDIX

- Support ADSL connection (with support PPPoE Protocol with PAP/CHAP Authentication mode)

- Supports 4 independent sockets simultaneously

- Not support IP Fragmentation

- Internal 16Kbytes Memory for Tx/Rx Buffers

- 0.18 μm CMOS technology

- 3.3V operation with 5V I/O signal tolerance

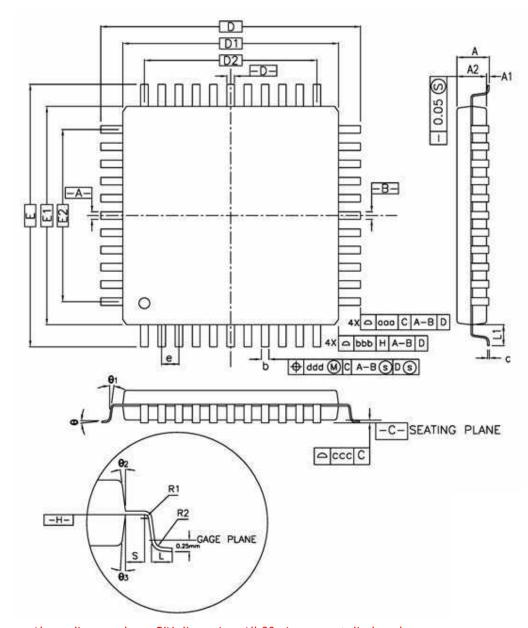

- Small 80 Pin LQFP Package

- Lead-Free Package

- Support Serial Peripheral Interface(SPI MODE 0, 3)

- Multi-function LED outputs (TX, RX, Full/Half duplex, Collision, Link, Speed)

### **Block Diagram**

### **Table of Contents**

| 1. Pin Assignment                                                            | 8  |

|------------------------------------------------------------------------------|----|

| 1.1 MCU Interface Signals                                                    | 9  |

| 1.2 PHY Signals                                                              | 10 |

| 1.3 Miscellaneous Signals                                                    | 11 |

| 1.4 Power Supply Signals                                                     | 12 |

| 1.5 Clock Signals                                                            | 12 |

| 1.6 LED Signals                                                              | 13 |

| 2. Memory Map                                                                | 14 |

| 3. W5100 Registers                                                           | 15 |

| 3.1 common registers                                                         | 15 |

| 3.2 Socket registers                                                         | 16 |

| 4. Register Descriptions                                                     | 20 |

| 4.1 Common Registers                                                         | 20 |

| 4.2 Socket Registers                                                         | 26 |

| 5. Functional Descriptions                                                   | 38 |

| 5.1 Initialization                                                           | 38 |

| 5.2.1 TCP                                                                    | 41 |

| 5.2.1.1 SERVER mode                                                          | 42 |

| 5.2.1.2 CLIENT mode                                                          | 49 |

| 5.2.2 UDP                                                                    | 51 |

| 5.2.3 IP raw                                                                 | 57 |

| 5.2.4 MAC raw                                                                | 58 |

| 6. Application Information                                                   | 60 |

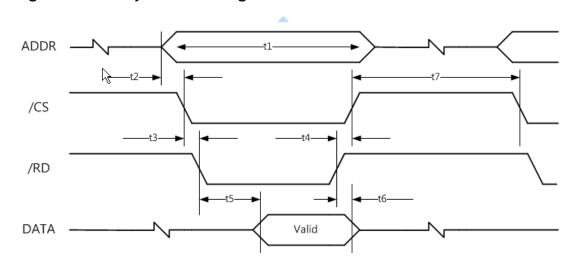

| 6.1 Direct Bus Interface mode                                                | 60 |

| 6.2 Indirect Bus Interface mode                                              | 60 |

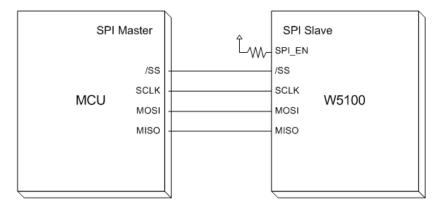

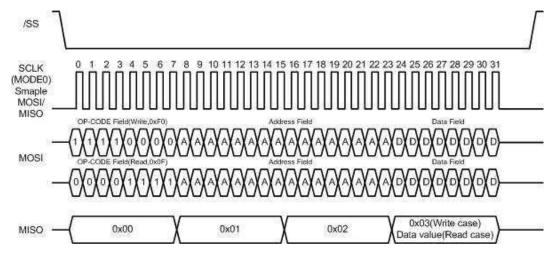

| 6.3 SPI (Serial Peripheral Interface) mode                                   | 61 |

| 6.3.1 Device Operations                                                      | 62 |

| 6.3.2 Commands                                                               | 62 |

| 6.3.3 Process of using general SPI Master device (According to SPI protocol) | 62 |

| 7. Electrical Specifications                                                 | 64 |

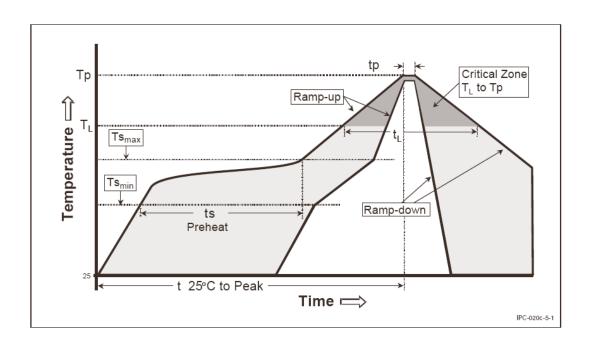

| 8. IR Reflow Temperature Profile (Lead-Free)                                 | 69 |

| Packago Doscriptions                                                         | 70 |

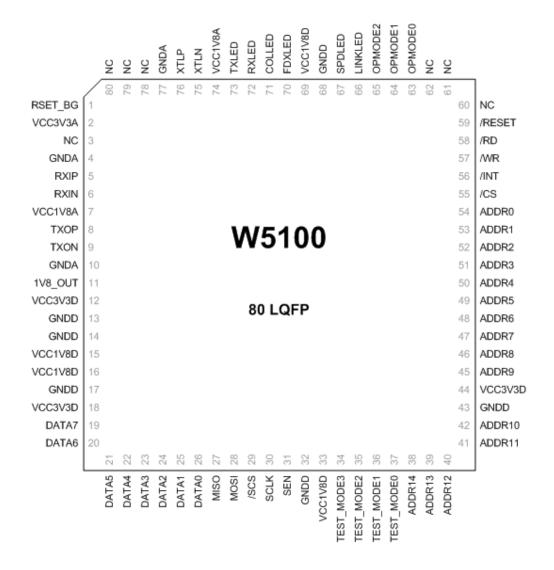

### 1. Pin Assignment

Pinout W5100

### 1.1 MCU Interface Signals

| Symbol   | Туре | Pin No     | Description                                                  |

|----------|------|------------|--------------------------------------------------------------|

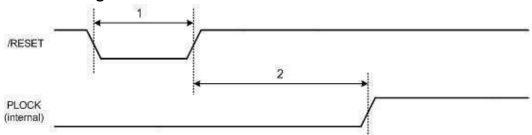

| /RESET   | I    | 59         | RESET                                                        |

|          |      |            | This pin is active Low input to initialize or re-initialize  |

|          |      |            | W5100.                                                       |

|          |      |            | By asserting this pin low for at least 2us, all internal     |

|          |      |            | registers will be re-initialized to their default states.    |

| ADDR14-0 | I    | 38,39,40   | ADDRESS                                                      |

|          |      | ,41,42,45  | These pins are used to select a register or memory.          |

|          |      | ,46,47,48  | Address pins are internally pulled down.                     |

|          |      | ,49,50,51  |                                                              |

|          |      | ,52, 53,54 |                                                              |

| DATA7-0  | 1/0  | 19, 20,    | DATA                                                         |

|          |      | 21, 22,    | These pins are used to read and write register or            |

|          |      | 23, 24,    | memory data.                                                 |

|          |      | 25, 26     |                                                              |

| /CS      | I    | 55         | CHIP SELECT                                                  |

|          |      |            | Chip Select is for MCU to access to internal registers or    |

|          |      |            | memory. /WR and /RD select direction of data transfer.       |

|          |      |            | This pin is active low.                                      |

| /INT     | 0    | 56         | INTERRUPT                                                    |

|          |      |            | This pin Indicates that W5100 requires MCU attention         |

|          |      |            | after socket connecting, disconnecting, data receiving or    |

|          |      |            | timeout. The interrupt is cleared by writing IR(Interrupt    |

|          |      |            | Register) or Sn_IR (Socket nth Interrupt Register). All      |

|          |      |            | interrupts are maskable. This pin is active low.             |

| /WR      | I    | 57         | WRITE ENABLE                                                 |

|          |      |            | Strobe from MCU to write an internal register/memory         |

|          |      |            | selected by ADDR[14:0]. Data is latched into the W5100       |

|          |      |            | on the rising edge of this input. This signal is active low. |

| /RD      | I    | 58         | READ ENABLE                                                  |

|          |      |            | Strobe from MCU to read an internal register/memory          |

|          |      |            | selected by ADDR[14:0]. This signal is active low.           |

| SEN      | I    | 31         | SPI ENABLE                                                   |

|          |      |            | This pin selects Enable/disable of the SPI Mode.             |

|          |      |            | Low = SPI Mode Disable                                       |

|      |   |    | High = SPI Mode Enable                                       |  |

|------|---|----|--------------------------------------------------------------|--|

|      |   |    | If you don't use SPI mode, then you tied this signal to      |  |

|      |   |    | '0'.                                                         |  |

| SCLK | I | 30 | SPI CLOCK                                                    |  |

|      |   |    | This pin is used to SPI Clock signal Pin.                    |  |

| /SCS | I | 29 | SPI SLAVE SELECT                                             |  |

|      |   |    | This pin is used to SPI Slave Select signal Pin. This pin is |  |

|      |   |    | active low                                                   |  |

| MOSI | I | 28 | SPI MASTER OUT SLAVE IN                                      |  |

|      |   |    | This pin is used to SPI MOSI signal pin.                     |  |

| MISO | 0 | 27 | SPI MASTER IN SLAVE OUT                                      |  |

|      |   |    | This pin is used to SPI MISO signal pin.                     |  |

## 1.2 PHY Signals

| Symbol    | Туре | Pin No  | Description                                               |  |  |

|-----------|------|---------|-----------------------------------------------------------|--|--|

| RXIP      | I    | 5       | RXIP/RXIN Signal Pair                                     |  |  |

|           |      |         | The differential data from the media is received on       |  |  |

| RXIN      | I    | 6       | the RXIP/RXIN signal pair.                                |  |  |

|           |      |         |                                                           |  |  |

| TXOP      | 0    | 8       | TXOP/TXON Signal Pair                                     |  |  |

| TXON      | 0    | 9       | The differential data is transmitted to the media on      |  |  |

| IXON      | 0    | ,       | the TXOP/TXIN signal pair.                                |  |  |

| RSET_BG   | 0    | 1       | PHY Off-chip resistor                                     |  |  |

|           |      |         | Connect a resistor of 12.3 $k\Omega\pm1\%$ to the ground. |  |  |

|           |      |         | Refer to the "Reference schematic".                       |  |  |

| OPMODE2-0 | 1    | 65, 64, | 4, OPERATION CONTROL MODE                                 |  |  |

|           |      | 63      | [2:0] Description                                         |  |  |

|           |      |         | 000 Auto-negotiation enable with all capabilities         |  |  |

|           |      |         | 001 Auto-negotiation with 100 BASE- X FDX/HDX ability     |  |  |

|           |      |         | 010 Auto-negotiation with 10 BASE-T FDX/HDX ability       |  |  |

|           |      |         | 011 Reserved                                              |  |  |

|           |      |         | 100 Manual selection of 100 BASE-TX FDX                   |  |  |

|           |      |         | 101 Manual selection of 100 BASE-TX HDX                   |  |  |

|           |      |         | 110 Manual selection of 10 BASE-T FDX                     |  |  |

|           |      |         | 111 Manual selection of 10 BASE-T HDX                     |  |  |

|           |      |         |                                                           |  |  |

## 1.3 Miscellaneous Signals

| Symbol       | Туре | Pin No  | Description                              |

|--------------|------|---------|------------------------------------------|

| TEST_MODE3-0 | I    | 34, 35, | W5100 MODE SELECT                        |

|              |      | 36, 37  | Normal mode : 0000                       |

|              |      |         | Other test modes are internal test mode. |

|              |      |         |                                          |

| NC           | 1/0  | 3, 60,  | NC                                       |

|              |      | 61, 62, | TEST PIN for W5100                       |

|              |      | 78, 79, | ( for factory use only)                  |

|              |      | 80      |                                          |

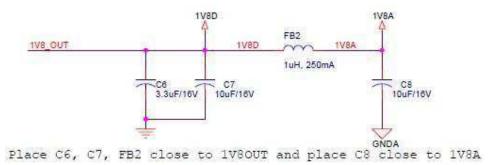

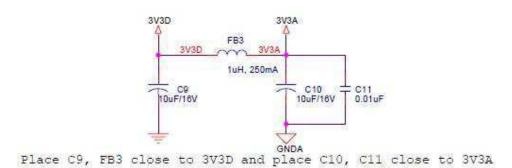

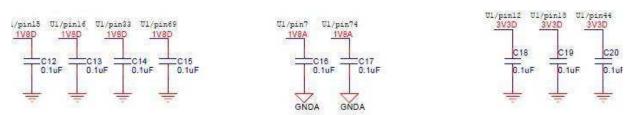

### 1.4 Power Supply Signals

| Symbol  | Туре   | Pin No     | Description                        |

|---------|--------|------------|------------------------------------|

| VCC3V3A | Power  | 2          | 3.3V power supply for Analog part  |

| VCC3V3D | Power  | 12, 18, 44 | 3.3V power supply for Digital part |

| VCC1V8A | Power  | 7, 74      | 1.8V power supply for Analog part  |

| VCC1V8D | Power  | 15, 16,    | 1.8V power supply for Digital part |

|         |        | 33, 69     |                                    |

| GNDA    | Ground | 4, 10, 77  | Analog ground                      |

| GNDD    | Ground | 13, 14,    | Digital ground                     |

|         |        | 17,        |                                    |

|         |        | 32, 43,    |                                    |

|         |        | 68,        |                                    |

| V18     | 0      | 11         | 1.8V regulator output voltage      |

ace C12, C13, C14, C15, C16, C17, C18, C19, C20 as close to each power pin as possibi

## 1.5 Clock Signals

| Symbol | Туре | Pin No | Description                                           |

|--------|------|--------|-------------------------------------------------------|

| XTLP   | 0    | 76     | 25MHz crystal input/output                            |

|        |      |        | A 25MHz parallel-resonant crystal is used to connect  |

| XTLN   | I    | 75     | these pins to stabilize the internal oscillator       |

|        |      |        | If you want to use oscillator, 25MHz clock to connect |

|        |      |        | XTLN signals and XTLP is open and MUST use 1.8V       |

|        |      |        | level oscillator.                                     |

### 1.6 LED Signals

| Symbol  | Туре | Pin No | Description                                          |

|---------|------|--------|------------------------------------------------------|

| LINKLED | 0    | 66     | Link LED                                             |

|         |      |        | Active low in link state indicates a good status for |

|         |      |        | 10/100M.                                             |

|         |      |        | It is always ON when the link is OK and it flashes   |

|         |      |        | while in a TX or RX state.                           |

| SPDLED  | 0    | 67     | Link speed LED                                       |

|         |      |        | Active low indicates the link speed is 100Mbps.      |

| FDXLED  | 0    | 70     | Full duplex LED                                      |

|         |      |        | Active low indicates the status of full-duplex mode. |

| COLLED  | 0    | 71     | Collision LED                                        |

|         |      |        | Active low indicates the presence of collision       |

|         |      |        | activity.                                            |

| RXLED   | 0    | 72     | Receive activity LED                                 |

|         |      |        | Active low indicates the presence of receiving       |

|         |      |        | activity.                                            |

| TXLED   | 0    | 73     | Transmit activity LED                                |

|         |      |        | Active low indicates the presence of transmitting    |

|         |      |        | activity.                                            |

### 2. Memory Map

W5100 is composed of Common Register, Socket Register, TX Memory, and RX Memory as shown below.

| 0x0000 | Common Registers |

|--------|------------------|

| 0x0030 | Reserved         |

| 0x0400 | Socket Registers |

| 0x0800 |                  |

|        | Reserved         |

| 0x4000 |                  |

|        | TX memory        |

| 0x6000 | RX memory        |

| 0x8000 |                  |

**Memory Map**

# 3. W5100 Registers3.1 common registers

| Address | Register                |

|---------|-------------------------|

| 0x0000  | Mode (MR)               |

|         | Gateway Address         |

| 0x0001  | (GAR0)                  |

| 0x0002  | (GAR1)                  |

| 0x0003  | (GAR2)                  |

| 0x0004  | (GAR3)                  |

|         | Subnet mask Address     |

| 0x0005  | (SUBRO)                 |

| 0x0006  | (SUBR1)                 |

| 0x0007  | (SUBR2)                 |

| 0x0008  | (SUBR3)                 |

|         | Source Hardware Address |

| 0x0009  | (SHAR0)                 |

| 0x000A  | (SHAR1)                 |

| 0x000B  | (SHAR2)                 |

| 0x000C  | (SHAR3)                 |

| 0x000D  | (SHAR4)                 |

| 0x000E  | (SHAR5)                 |

|         | Source IP Address       |

| 0x000F  | (SIPRO)                 |

| 0x0010  | (SIPR1)                 |

| 0x0011  | (SIPR2)                 |

| 0x0012  | (SIPR3)                 |

| 0x0013  | Reserved                |

| 0x0014  |                         |

| 0x0015  | Interrupt (IR)          |

| 0x0016  | Interrupt Mask (IMR)    |

|         | Retry Time              |

| 0x0017  | (RTRO)                  |

| 0x0018  | (RTR1)                  |

| 0x0019  | Retry Count (RCR)       |

| Address | Register                     |  |  |

|---------|------------------------------|--|--|

| 0x001A  | RX Memory Size (RMSR)        |  |  |

| 0x001B  | TX Memory Size (TMSR)        |  |  |

|         | Authentication Type in PPPoE |  |  |

| 0x001C  | (PATRO)                      |  |  |

| 0x001D  | (PATR1)                      |  |  |

| 0x001E  |                              |  |  |

| ~       | Reserved                     |  |  |

| 0x0027  |                              |  |  |

| 0x0028  | PPP LCP Request Timer        |  |  |

|         | (PTIMER)                     |  |  |

| 0x0029  | PPP LCP Magic number         |  |  |

|         | (PMAGIC)                     |  |  |

|         | Unreachable IP Address       |  |  |

| 0x002A  | (UIPRO)                      |  |  |

| 0x002B  | (UIPR1)                      |  |  |

| 0x002C  | (UIPR2)                      |  |  |

| 0x002D  | (UIPR3)                      |  |  |

|         | Unreachable Port             |  |  |

| 0x002E  | (UPORTO)                     |  |  |

| 0x002F  | (UPORT1)                     |  |  |

| 0x0030  |                              |  |  |

| ~       | Reserved                     |  |  |

| 0x03FF  |                              |  |  |

|         |                              |  |  |

## 3.2 Socket registers

| Address | Register                              | Address | Register                  |

|---------|---------------------------------------|---------|---------------------------|

| 0x0400  | Socket 0 Mode (S0_MR)                 | 0x0415  | Socket 0 IP TOS (S0_TOS)  |

| 0x0401  | Socket 0 Command (S0_CR)              | 0x0416  | Socket 0 IP TTL (S0_TTL)  |

| 0x0402  | Socket 0 Interrupt (SO_IR)            | 0x0417  |                           |

| 0x0403  | Socket 0 Status (S0_SR)               | ~       | Reserved                  |

|         | Socket 0 Source Port                  | 0x041F  |                           |

| 0x0404  | (SO_PORTO)                            |         | Socket 0 TX Free Size     |

| 0x0405  | (SO_PORT1)                            | 0x0420  | (S0_TX_FSR0)              |

|         | Socket 0 Destination Hardware Address | 0x0421  | (S0_TX_FSR1)              |

| 0x0406  | (SO_DHAR0)                            |         | Socket 0 TX Read Pointer  |

| 0x0407  | (SO_DHAR1)                            | 0x0422  | (S0_TX_RD0)               |

| 0x0408  | (SO_DHAR2)                            | 0x0423  | (SO_TX_RD1)               |

| 0x0409  | (SO_DHAR3)                            |         | Socket 0 TX Write Pointer |

| 0x040A  | (SO_DHAR4)                            | 0x0424  | (S0_TX_WR0)               |

| 0x040B  | (SO_DHAR5)                            | 0x0425  | (S0_TX_WR1)               |

|         | Socket 0 Destination IP Address       |         | Socket 0 RX Received Size |

| 0x040C  | (SO_DIPRO)                            | 0x0426  | (S0_RX_RSR0)              |

| 0x040D  | (SO_DIPR1)                            | 0x0427  | (S0_RX_RSR1)              |

| 0x040E  | (SO_DIPR2)                            |         | Socket 0 RX Read Pointer  |

| 0x040F  | (SO_DIPR3)                            | 0x0428  | (SO_RX_RD0)               |

|         | Socket 0 Destination Port             | 0x0429  | (SO_RX_RD1)               |

| 0x0410  | (SO_DPORT0)                           | 0x042A  | Reserved                  |

| 0x0411  | (SO_DPORT1)                           | 0x042B  |                           |

|         | Socket 0 Maximum Segment Size         | 0x042C  |                           |

| 0x0412  | (SO_MSSRO)                            | ~       | Reserved                  |

| 0x0413  | (SO_MSSR1)                            | 0x04FF  |                           |

|         | Socket 0 Protocol in IP Raw mode      | _       |                           |

| 0x0414  | (S0_PROTO)                            |         |                           |

| Address | Register                              | Address | Register                  |

|---------|---------------------------------------|---------|---------------------------|

| 0x0500  | Socket 1 Mode (S1_MR)                 | 0x0515  | Socket 1 IP TOS (S1_TOS)  |

| 0x0501  | Socket 1 Command (S1_CR)              | 0x0516  | Socket 1 IP TTL (S1_TTL)  |

| 0x0502  | Socket 1 Interrupt (S1_IR)            | 0x0517  |                           |

| 0x0503  | Socket 1 Status (S1_SR)               | ~       | Reserved                  |

|         | Socket 1 Source Port                  | 0x051F  |                           |

| 0x0504  | (S1_PORT0)                            |         | Socket 1 TX Free Size     |

| 0x0505  | (S1_PORT1)                            | 0x0520  | (S1_TX_FSR0)              |

|         | Socket 1 Destination Hardware Address | 0x0521  | (S1_TX_FSR1)              |

| 0x0506  | (S1_DHAR0)                            |         | Socket 1 TX Read Pointer  |

| 0x0507  | (S1_DHAR1)                            | 0x0522  | (S1_TX_RD0)               |

| 0x0508  | (S1_DHAR2)                            | 0x0523  | (S1_TX_RD1)               |

| 0x0509  | (S1_DHAR3)                            |         | Socket 1 TX Write Pointer |

| 0x050A  | (S1_DHAR4)                            | 0x0524  | (S1_TX_WR0)               |

| 0x050B  | (S1_DHAR5)                            | 0x0525  | (S1_TX_WR1)               |

|         | Socket 1 Destination IP Address       |         | Socket 1 RX Received Size |

| 0x050C  | (S1_DIPR0)                            | 0x0526  | (S1_RX_RSR0)              |

| 0x050D  | (S1_DIPR1)                            | 0x0527  | (S1_RX_RSR1)              |

| 0x050E  | (S1_DIPR2)                            |         | Socket 1 RX Read Pointer  |

| 0x050F  | (S1_DIPR3)                            | 0x0528  | (S1_RX_RD0)               |

|         | Socket 1 Destination Port             | 0x0529  | (S1_RX_RD1)               |

| 0x0510  | (S1_DPORT0)                           | 0x052A  | Reserved                  |

| 0x0511  | (S1_DPORT1)                           | 0x052B  |                           |

|         | Socket 1 Maximum Segment Size         | 0x052C  |                           |

| 0x0512  | (S1_MSSRO)                            | ~       | Reserved                  |

| 0x0513  | (S1_MSSR1)                            | 0x05FF  |                           |

|         | Socket 1 Protocol in IP Raw mode      |         | •                         |

| 0x0514  | (S1_PROTO)                            |         |                           |

| Address | Register                              | Address | Register                  |

|---------|---------------------------------------|---------|---------------------------|

| 0x0600  | Socket 2 Mode (S2_MR)                 | 0x0615  | Socket 2 IP TOS (S2_TOS)  |

| 0x0601  | Socket 2 Command (S2_CR)              | 0x0616  | Socket 2 IP TTL (S2_TTL)  |

| 0x0602  | Socket 2 Interrupt (S2_IR)            | 0x0617  |                           |

| 0x0603  | Socket 2 Status (S2_SR)               | ~       | Reserved                  |

|         | Socket 2 Source Port                  | 0x061F  |                           |

| 0x0604  | (S2_PORT0)                            |         | Socket 2 TX Free Size     |

| 0x0605  | (S2_PORT1)                            | 0x0620  | (S2_TX_FSR0)              |

|         | Socket 2 Destination Hardware Address | 0x0621  | (S2_TX_FSR1)              |

| 0x0606  | (S2_DHAR0)                            |         | Socket 2 TX Read Pointer  |

| 0x0607  | (S2_DHAR1)                            | 0x0622  | (S2_TX_RD0)               |

| 0x0608  | (S2_DHAR2)                            | 0x0623  | (S2_TX_RD1)               |

| 0x0609  | (S2_DHAR3)                            |         | Socket 2 TX Write Pointer |

| 0x060A  | (S2_DHAR4)                            | 0x0624  | (S2_TX_WR0)               |

| 0x060B  | (S2_DHAR5)                            | 0x0625  | (S2_TX_WR1)               |

|         | Socket 2 Destination IP Address       |         | Socket 2 RX Received Size |

| 0x060C  | (S2_DIPR0)                            | 0x0626  | (S2_RX_RSR0)              |

| 0x060D  | (S2_DIPR1)                            | 0x0627  | (S2_RX_RSR1)              |

| 0x060E  | (S2_DIPR2)                            |         | Socket 2 RX Read Pointer  |

| 0x060F  | (S2_DIPR3)                            | 0x0628  | (S2_RX_RD0)               |

|         | Socket 2 Destination Port             | 0x0629  | (S2_RX_RD1)               |

| 0x0610  | (S2_DPORT0)                           | 0x062A  | Reserved                  |

| 0x0611  | (S2_DPORT1)                           | 0x062B  |                           |

|         | Socket 2 Maximum Segment Size         | 0x062C  |                           |

| 0x0612  | (S2_MSSR0)                            | ~       | Reserved                  |

| 0x0613  | (S2_MSSR1)                            | 0x06FF  |                           |

|         | Socket 2 Protocol in IP Raw mode      | -       | •                         |

| 0x0614  | (S2_PROTO)                            |         |                           |

| Address | Register                              | Address | Register                  |

|---------|---------------------------------------|---------|---------------------------|

| 0x0700  | Socket 3 Mode (S3_MR)                 | 0x0715  | Socket 3 IP TOS (S3_TOS)  |

| 0x0701  | Socket 3 Command (S3_CR)              | 0x0716  | Socket 3 IP TTL (S3_TTL)  |

| 0x0702  | Socket 3 Interrupt (S3_IR)            | 0x0717  |                           |

| 0x0703  | Socket 3 Status (S3_SR)               | ~       | Reserved                  |

|         | Socket 3 Source Port                  | 0x071F  |                           |

| 0x0704  | (S3_PORT0)                            |         | Socket 3 TX Free Size     |

| 0x0705  | (S3_PORT1)                            | 0x0720  | (S3_TX_FSR0)              |

|         | Socket 3 Destination Hardware Address | 0x0721  | (S3_TX_FSR1)              |

| 0x0706  | (S3_DHARO)                            |         | Socket 3 TX Read Pointer  |

| 0x0707  | (S3_DHAR1)                            | 0x0722  | (S3_TX_RD0)               |

| 0x0708  | (S3_DHAR2)                            | 0x0723  | (S3_TX_RD1)               |

| 0x0709  | (S3_DHAR3)                            |         | Socket 3 TX Write Pointer |

| 0x070A  | (S3_DHAR4)                            | 0x0724  | (S3_TX_WR0)               |

| 0x070B  | (S3_DHAR5)                            | 0x0725  | (S3_TX_WR1)               |

|         | Socket 3 Destination IP Address       |         | Socket 3 RX Received Size |

| 0x070C  | (S3_DIPRO)                            | 0x0726  | (S3_RX_RSR0)              |

| 0x070D  | (S3_DIPR1)                            | 0x0727  | (S3_RX_RSR1)              |

| 0x070E  | (S3_DIPR2)                            |         | Socket 3 RX Read Pointer  |

| 0x070F  | (S3_DIPR3)                            | 0x0728  | (S3_RX_RD0)               |

|         | Socket 3 Destination Port             | 0x0729  | (S3_RX_RD1)               |

| 0x0710  | (S3_DPORT0)                           | 0x072A  | Reserved                  |

| 0x0711  | (S3_DPORT1)                           | 0x072B  |                           |

|         | Socket 3 Maximum Segment Size         | 0x072C  |                           |

| 0x0712  | (S3_MSSRO)                            | ~       | Reserved                  |

| 0x0713  | (S3_MSSR1)                            | 0x07FF  |                           |

|         | Socket 3 Protocol in IP Raw mode      | -       | •                         |

| 0x0714  | (S3_PROTO)                            |         |                           |

### 4. Register Descriptions

### 4.1 Common Registers

#### MR (Mode Register) [R/W] [0x0000] [0x00]

This register is used for S/W reset, ping block mode, PPPoE mode and Indirect bus I/F.

| 7   | 6 | 5 | 4  | 3     | 2 | 1  | 0   |   |

|-----|---|---|----|-------|---|----|-----|---|

| RST |   |   | PB | PPPoE |   | Al | IND | ı |

| Bit | Symbol   | Description                                                                         |

|-----|----------|-------------------------------------------------------------------------------------|

|     |          | S/W Reset                                                                           |

| 7   | RST      | If this bit is '1', internal register will be initialized. It will be automatically |

| -   |          | cleared after reset.                                                                |

| 6   | Reserved | Reserved                                                                            |

| 5   | Reserved | Reserved                                                                            |

|     |          | Ping Block Mode                                                                     |

| 4   | DD.      | 0 : Disable Ping block                                                              |

| 4   | PB       | 1 : Enable Ping block                                                               |

|     |          | If the bit is set as '1', there is no response to the ping request.                 |

|     |          | PPPoE Mode                                                                          |

|     |          | 0 : Disable PPPoE mode                                                              |

|     |          | 1 : Enable PPPoE mode                                                               |

| 3   | PPPoE    | If you use ADSL without router or etc, you should set the bit as '1' to             |

|     |          | connect to ADSL Server. For more detail, refer to the application note,             |

|     |          | "How to connect ADSL".                                                              |

|     |          |                                                                                     |

| 2   | Not Used | Not Used                                                                            |

|     |          | Address Auto-Increment in Indirect Bus I/F                                          |

|     |          | 0 : Disable auto-increment                                                          |

|     |          | 1 : Enable auto-increment                                                           |

| 1   | Al       | At the Indirect Bus I/F mode, if this bit is set as '1', the address will be        |

|     |          | automatically increased by 1 whenever read and write are performed. For             |

|     |          | more detail, refer to "6.2 Indirect Bus IF Mode".                                   |

| 0   | IND      | Indirect Bus I/F mode                                                               |

| 0 : Disable Indirect bus I/F mode                                               |

|---------------------------------------------------------------------------------|

| 1 : Enable Indirect bus I/F mode                                                |

| If this bit is set as '1', Indirect BUS I/F mode is set. For more detail, refer |

| to "6. Application Information", "6.2 Indirect Bus IF Mode".                    |

#### GWR (Gateway IP Address Register) [R/W] [0x0001 - 0x0004] [0x00]

This Register sets up the default gateway address.

Ex) in case of "192.168.0.1"

| 0x0001                | 0x0002 | 0x0003   | 0x0004   |  |  |

|-----------------------|--------|----------|----------|--|--|

| 192 (0xC0) 168 (0xA8) |        | 0 (0x00) | 1 (0x01) |  |  |

#### SUBR (Subnet Mask Register) [R/W] [0x0005 - 0x0008] [0x00]

This register sets up the subnet mask address.

Ex) in case of "255.255.255.0"

| 0x0005     | 0x0006                | 0x0007 | 0x0008   |  |  |

|------------|-----------------------|--------|----------|--|--|

| 255 (0xFF) | 255 (0xFF) 255 (0xFF) |        | 0 (0x00) |  |  |

#### SHAR (Source Hardware Address Register) [R/W] [0x0009 - 0x000E] [0x00]

This register sets up the Source Hardware address.

Ex) In case of "00.08.DC.01.02.03"

| 0x0009 | 0x000A | 0x000B | 0x000C | 0x000D | 0x000E |

|--------|--------|--------|--------|--------|--------|

| 0x00   | 0x08   | 0xDC   | 0x01   | 0x02   | 0x03   |

#### SIPR (Source IP Address Register) [R/W] [0x000F - 0x0012] [0x00]

This register sets up the Source IP address.

Ex) in case of "192.168.0.3"

| 0x000F     | 0x0010     | 0x0011   | 0x0012   |  |

|------------|------------|----------|----------|--|

| 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 3 (0x03) |  |

#### IR (Interrupt Register) [R] [0x0015] [0x00]

This register is accessed by the host processor to know the cause of an interrupt.

Any interrupt can be masked in the Interrupt Mask Register (IMR). The /INT signal retain low as long as any masked signal is set, and will not go high until all masked bits in this Register have been cleared.

| 7        | 6       | 5     | 4        | 3      | 2      | 1      | 0      |

|----------|---------|-------|----------|--------|--------|--------|--------|

| CONFLICT | UNREACH | PPPoE | Reserved | S3_INT | S2_INT | S1_INT | S0_INT |

| Bit | Symbol   | Description                                                                   |

|-----|----------|-------------------------------------------------------------------------------|

|     |          | IP Conflict                                                                   |

| 7   | CONFLICT | It is set as '1', when there is ARP request with same IP address as Source IP |

|     |          | address. This bit is cleared to '0' by writing '1' to this bit.               |

|     |          | Destination unreachable                                                       |

|     |          | W5100 will receive ICMP(Destination Unreachable) packet if non-existing       |

|     |          | destination IP address is transmitted during UDP data transmission. (Refer    |

| 6   | UNREACH  | to "5.2.2 UDP"). In this case, the IP address and the port number will be     |

|     |          | saved in Unreachable IP Address (UIPR) and Unreachable Port Register          |

|     |          | (UPORT), and the bit will be set as '1'. This bit will be cleared to '0' by   |

|     |          | writing '1' to this bit.                                                      |

|     |          | PPPoE Connection Close                                                        |

| 5   | PPPoE    | In the PPPoE Mode, if the PPPoE connection is closed, '1' is set. This bit    |

|     |          | will be cleared to '0' by writing '1' to this bit.                            |

| 4   | Reserved | Reserved                                                                      |

|     |          | Occurrence of Socket 3 Socket Interrupt                                       |

|     |          | It is set in case that interrupt occurs at the socket 3. For more detailed    |

| 3   | S3_INT   | information of socket interrupt, refer to "Socket 3 Interrupt Register        |

|     |          | (S3_IR)". This bit will be automatically cleared when S3_IR is cleared to     |

|     |          | 0x00.                                                                         |

|     |          | Occurrence of Socket 2 Socket Interrupt                                       |

|     |          | It is set in case that interrupt occurs at the socket 2. For more detailed    |

| 2   | S2_INT   | information of socket interrupt, refer to "Socket 2 Interrupt                 |

|     |          | Register(S2_IR)". This bit will be automatically cleared when S2_IR is        |

|     |          | cleared to 0x00.                                                              |

|     |          | Occurrence of Socket 1 Socket Interrupt                                       |

| 1   | S1_INT   | It is set in case that interrupt occurs at the socket 1. For more detailed    |

|     |          | information of socket interrupt, refer to "Socket 1 Interrupt Register        |

|   |        | (S1_IR)". This bit will be automatically cleared when S1_IR is cleared to  |

|---|--------|----------------------------------------------------------------------------|

|   |        | 0x00.                                                                      |

|   |        | Occurrence of Socket 0 Socket Interrupt                                    |

|   | S0_INT | It is set in case that interrupt occurs at the socket 0. For more detailed |

| 0 |        | information of socket interrupt, refer to "Socket 0 Interrupt Register     |

|   |        | (SO_IR)". This bit will be automatically cleared when SO_IR is cleared to  |

|   |        | 0x00.                                                                      |

#### IMR (Interrupt Mask Register) [R/W] [0x0016] [0x00]

The Interrupt Mask Register is used to mask interrupts. Each interrupt mask bit corresponds to a bit in the Interrupt Register (IR). If an interrupt mask bit is set, an interrupt will be issued whenever the corresponding bit in the IR is set. If any bit in the IMR is set as '0', an interrupt will not occur though the bit in the IR is set.

| 7      | 6      | 5      | 4        | 3      | 2      | 1      | 0      |

|--------|--------|--------|----------|--------|--------|--------|--------|

| IM_IR7 | IM_IR6 | IM_IR5 | Reserved | IM_IR3 | IM_IR2 | IM_IR1 | IM_IR0 |

| Bit | Symbol   | Description                                    |

|-----|----------|------------------------------------------------|

| 7   | IM_IR7   | IP Conflict Enable                             |

| 6   | IM_IR6   | Destination unreachable Enable                 |

| 5   | IM_IR5   | PPPoE Close Enable                             |

| 4   | Reserved | It should be set as '0'                        |

| 3   | IM_IR3   | Occurrence of Socket 3 Socket Interrupt Enable |

| 2   | IM_IR2   | Occurrence of Socket 2 Socket Interrupt Enable |

| 1   | IM_IR1   | Occurrence of Socket 1 Socket Interrupt Enable |

| 0   | IM_IR0   | Occurrence of Socket 0 Socket Interrupt Enable |

#### RTR (Retry Time-value Register) [R/W] [0x0017 - 0x0018] [0x07D0]

This register sets the period of timeout. Value 1 means 100us. The initial value is 2000(0x07D0). That will be set as 200ms.

#### Ex) For 400ms configuration, set as 4000(0x0FA0)

| 0x0017 | 0x0018 |

|--------|--------|

| 0x0F   | 0xA0   |

Re-transmission will occur if there is no response from the remote peer to the commands of CONNECT, DISCON, CLOSE, SEND, SEND\_MAC and SEND\_KEEP, or the response is delayed.

#### RCR (Retry Count Register) [R/W] [0x0019] [0x08]

This register sets the number of re-transmission. If retransmission occurs more than the number recorded in RCR, Timeout Interrupt (TIMEOUT bit of Socket n Interrupt Register (Sn\_IR) is set as '1') will occur.

#### RMSR(RX Memory Size Register) [R/W] [0x001A] [0x55]

This register assigns total 8K RX Memory to each socket.

| 7  | 6        | 5  | 4     | 3    | 2     | 1    | 0     |

|----|----------|----|-------|------|-------|------|-------|

| S  | Socket 3 |    | ket 2 | Soci | ket 1 | Sock | ket 0 |

| S1 | S0       | S1 | S0    | S1   | S0    | S1   | SO    |

The memory size according to the configuration of S1, S0, is as below.

| <b>S</b> 1 | S0      | Memory size |  |  |  |

|------------|---------|-------------|--|--|--|

| 0          | 0       | 1KB         |  |  |  |

| 0          | 1       | 2KB         |  |  |  |

| 1          | 1 0 4KB |             |  |  |  |

| 1          | 1       | 8KB         |  |  |  |

According to the value of S1 and S0, the memory is assigned to the sockets from socket 0 within the range of 8KB. If there is not enough memory to be assigned, the socket should not be used. The initial value is 0x55 and the 2K memory is assigned to each 4 sockets respectively.

Ex) When setting as 0xAA, the 4KB memory should be assigned to each socket.

However, the total memory size is 8KB. The memory is normally assigned to the socket 0 and 1, but not to the socket 2 and 3. Therefore, socket 2 and 3 can not be absolutely used.

| Socket 3 | Socket 3 Socket 2 |     | Socket 0 |  |

|----------|-------------------|-----|----------|--|

| 0KB      | 0KB               | 4KB | 4KB      |  |

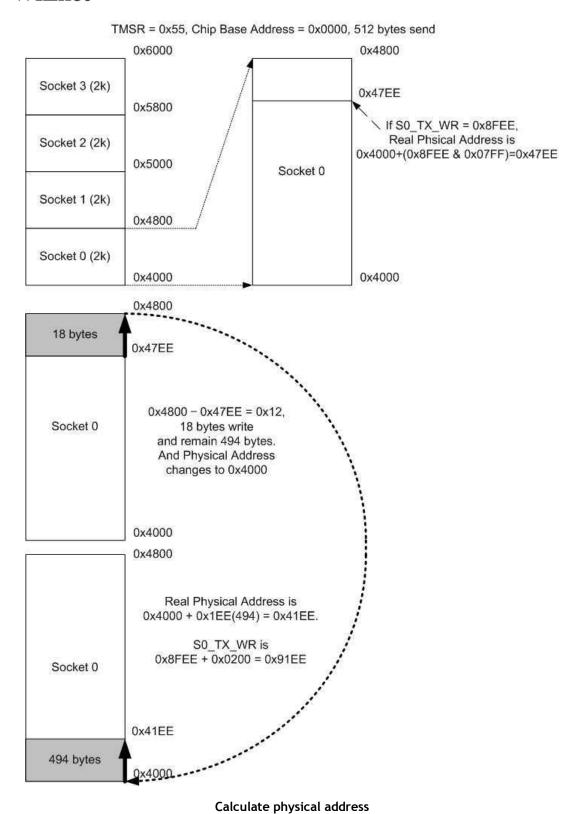

#### TMSR(TX Memory Size Register) [R/W] [0x001B] [0x55]

This register is used in assigning total 8K TX Memory to sockets. Configuration can be done in the same way of RX Memory Size Register (RMSR). The initial value is 0x55 and it is to assign 2K memory to 4 sockets respectively.

#### PATR (Authentication Type in PPPoE mode) [R] [0x001C-0x001D] [0x0000]

This register notifies authentication method that has been agreed at the connection with PPPoE Server. W5100 supports two types of Authentication method - PAP and CHAP.

| Value  | Authentication Type |  |  |

|--------|---------------------|--|--|

| 0xC023 | PAP                 |  |  |

| 0xC223 | СНАР                |  |  |

#### PTIMER (PPP Link Control Protocol Request Timer Register) [R/W] [0x0028] [0x28]

This register indicates the duration for sending LCP Echo Request. Value 1 is about 25ms.

Ex) in case that PTIMER is 200, 200 \* 25(ms) = 5000(ms) = 5 seconds

#### PMAGIC (PPP Link Control Protocol Magic number Register) [R/W] [0x0029] [0x00]

This register is used in Magic number option during LCP negotiation. Refer to the application note, "How to connect ADSL".

#### UIPR (Unreachable IP Address Register) [R] [0x002A - 0x002D] [0x00]

In case of data transmission using UDP (refer to "5.2.2. UDP"), if transmitting to non-existing IP address, ICMP (Destination Unreachable) packet will be received. In this case, that IP address and port number will be saved in the Unreachable IP Address Register(UIPR) and Unreachable Port Register(UPORT) respectively.

Ex) in case of "192.168.0.11",

| 0x002A     | 0x002B     | 0x002C   | 0x002D    |  |

|------------|------------|----------|-----------|--|

| 192 (0xC0) | 168 (0xA8) | 0 (0x00) | 11 (0x0B) |  |

#### UPORT (Unreachable Port Register) [R] [0x002E - 0x002F] [0x0000]

Refer to Unreachable IP Address Register (UIPR)

Ex) In case of 5000(0x1388),

| 0x002E | 0x002F |  |  |

|--------|--------|--|--|

| 0x13   | 0x88   |  |  |

© Copyright 2009-2010 WIZnet Co., Inc. All rights reserved.

### 4.2 Socket Registers

$Sn^{1}$ \_MR (Socket *n* Mode Register) [R/W] [0x0400, 0x0500, 0x0600, 0x0700] [0x00]<sup>2</sup>

This register sets up socket option or protocol type for each socket.

| 7     | 6 | 5       | 4 | 3  | 2  | 1  | 0  |

|-------|---|---------|---|----|----|----|----|

| MULTI |   | ND / MC |   | P3 | P2 | P1 | P0 |

| Bit | Symbol   |                                                                             |                                                |          |          | Description                                     |  |  |

|-----|----------|-----------------------------------------------------------------------------|------------------------------------------------|----------|----------|-------------------------------------------------|--|--|

|     |          | Multica                                                                     | sting                                          |          |          |                                                 |  |  |

|     |          | 0 : disable Multicasting                                                    |                                                |          |          |                                                 |  |  |

|     |          | 1 : enab                                                                    | ole Multi                                      | icasting |          |                                                 |  |  |

| 7   | 7 MULTI  | It is app                                                                   | It is applied only in case of UDP.             |          |          |                                                 |  |  |

|     |          | For usin                                                                    | g multio                                       | casting, | write m  | nulticast group address to Socket n Destination |  |  |

|     |          | IP and                                                                      | multicas                                       | st group | port n   | umber to Socket $n$ Destination Port Register,  |  |  |

|     |          | before (                                                                    | OPEN co                                        | mmand    |          |                                                 |  |  |

| 6   | Reserved | Reserve                                                                     | d                                              |          |          |                                                 |  |  |

|     |          | Use No                                                                      | Delayed                                        | d ACK    |          |                                                 |  |  |

|     |          | 0 : Disal                                                                   | ole No D                                       | elayed . | ACK opt  | ion                                             |  |  |

|     |          | 1 : Enab                                                                    | le No D                                        | elayed A | ACK opti | on,                                             |  |  |

|     |          | It is applied only in case of TCP. If this bit is set as '1', ACK packet is |                                                |          |          |                                                 |  |  |

|     |          | transmitted whenever receiving data packet from the peer. If this bit is    |                                                |          |          |                                                 |  |  |

| 5   | ND/MC    | cleared to '0', ACK packet is transmitted according to internal Timeout     |                                                |          |          |                                                 |  |  |

|     |          | mechanism.                                                                  |                                                |          |          |                                                 |  |  |

|     |          | Multicast                                                                   |                                                |          |          |                                                 |  |  |

|     |          | 0: using IGMP version 2                                                     |                                                |          |          |                                                 |  |  |

|     |          | 1 : using                                                                   | g IGMP v                                       | ersion 1 | I        |                                                 |  |  |

|     |          | It is app                                                                   | It is applied only in case of MULTI bit is '1' |          |          |                                                 |  |  |

| 4   | Reserved | Reserved                                                                    |                                                |          |          |                                                 |  |  |

|     |          | Protoco                                                                     | ol                                             |          |          |                                                 |  |  |

| 3   | P3       | Sets up                                                                     | corresp                                        | onding s | ocket a  | s TCP, UDP, or IP RAW mode                      |  |  |

|     |          | P3                                                                          | P2                                             | P1       | P0       | Meaning                                         |  |  |

|     | B0       | 0                                                                           | 0                                              | 0        | 0        | Closed                                          |  |  |

| 2   | P2       | 0                                                                           | 0                                              | 0        | 1        | ТСР                                             |  |  |

|     |          | -                                                                           |                                                |          |          |                                                 |  |  |

<sup>&</sup>lt;sup>1</sup> *n* is socket number (0, 1, 2, 3).

<sup>&</sup>lt;sup>2</sup> [Read/Write] [address of socket 0, address of socket 1, address of socket 2, address of socket 3] [Reset value]

|   |    | 0        | 0        | 1               | 0             | UDP                   |

|---|----|----------|----------|-----------------|---------------|-----------------------|

| 1 | P1 | 0        | 0        | 1               | 1             | IPRAW                 |

|   |    |          |          |                 |               |                       |

|   |    | * In cas | e of soc | ket 0, <i>l</i> | <b>MACRAW</b> | and PPPoE mode exist. |

| 0 | P0 | Р3       | P2       | P1              | P0            | Meaning               |

| O | 10 | 0        | 1        | 0               | 0             | MACRAW                |

|   |    | 0        | 1        | 0               | 1             | PPPoE                 |

#### Sn\_CR (Socket n Command Register) [R/W] [0x0401, 0x0501, 0x0601, 0x0701] [0x00]

This register is utilized for socket n initialization, close, connection establishment, termination, data transmission and command receipt. After performing the commands, the register value will be automatically cleared to 0x00.

| Value | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01  | OPEN    | It is used to initialize the socket. According to the value of Socket $n$ Mode Register (Sn_MR), Socket $n$ Status Register(Sn_SR) value is                                                                                                                                                                                                                             |

| 0.01  | OI LIV  | changed to SOCK_INIT, SOCK_UDP, SOCK_IPRAW, or SOCK_MACRAW.  For more detail, refer to 5. Functional Description.                                                                                                                                                                                                                                                       |

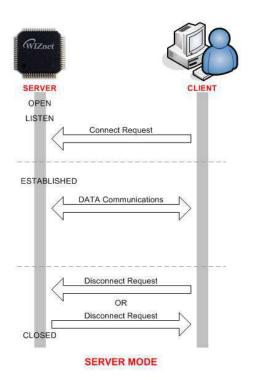

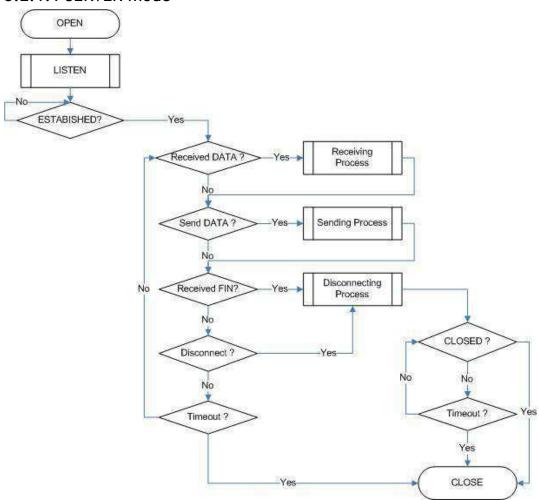

| 0x02  | LISTEN  | It is only used in TCP mode.  It changes the value of Socket <i>n</i> Status Register (Sn_SR) to SOCK_LISTEN in order to wait for a connection request from any remote peer (TCP Client).  For more detail, refer to 5.2.1.1 SERVER mode.                                                                                                                               |

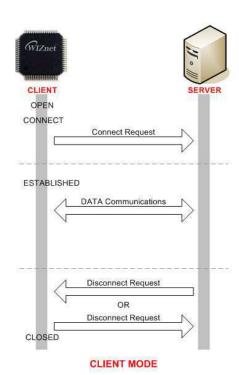

| 0x04  | CONNECT | It is only used in TCP mode.  It sends a connection request to remote peer(TCP SERVER). If the connection is failed, Timeout interrupt will occur.  For more detail, refer to 5.2.1.2 CLIENT mode.                                                                                                                                                                      |

| 0x08  | DISCON  | It is only used in TCP mode.  It sends a connection termination request. If connection termination is failed, Timeout interrupt will occur. For more detail, refer to 5.2.1.1 SERVER mode.  * In case of using CLOSE command instead of DISCON, only the value of Socket n Status Register(Sn_SR) is changed to SOCK_CLOSED without the connection termination process. |

| 0x10  | CLOSE   | It is used to close the socket. It changes the value of Socket $n$ Status Register( $Sn_SR$ ) to SOCK_CLOSED.                                                                                                                                                                                                                                                           |

|      |           | It transmits the data as much as the increased size of Socket $n$ TX Write      |

|------|-----------|---------------------------------------------------------------------------------|

| 0x20 | SEND      | Pointer. For more detail, refer to Socket <i>n</i> TX Free Size Register        |

|      | SEND      | (Sn_TX_FSR), Socket n TX Write Pointer Register(Sn_TX_WR), and Socket           |

|      |           | n TX Read Pointer Register(Sn_TX_RR) or 5.2.1.1. SERVER mode.                   |

| •    |           | It is used in UDP mode.                                                         |

|      |           | The basic operation is same as SEND. Normally SEND operation needs              |

| 0x21 | SEND_MAC  | Destination Hardware Address that is received in ARP(Address Resolution         |

|      |           | Protocol) process. SEND_MAC uses Socket <i>n</i> Destination Hardware           |

|      |           | Address(Sn_DHAR) that is written by users without ARP process.                  |

|      |           | It is only used in TCP mode.                                                    |

|      | SEND_KEEP | It checks the connection status by sending 1byte data. If the connection        |

| 0x22 |           | is already terminated or peer has no response, Timeout interrupt will           |

|      |           | occur.                                                                          |

|      | RECV      | Receiving is processed with the value of Socket n RX Read Pointer               |

|      |           | Register(Sn_RX_RD).                                                             |

|      |           | For more detail, refer to 5.2.1.1 SERVER mode Receiving Process with            |

| 0x40 |           | Socket <i>n</i> RX Received Size Register (Sn_RX_RSR), Socket <i>n</i> RX Write |

|      |           | Pointer Register(Sn_RX_WR), and Socket n RX Read Pointer                        |

|      |           | Register(Sn_RX_RD)                                                              |

|      |           | 1 2 , /                                                                         |

#### Sn\_IR (Socket n Interrupt Register) [R] [0x0402, 0x0502, 0x0602, 0x0702] [0x00]

This register is used for notifying connection establishment and termination, receiving data and Timeout. The Socket n Interrupt Register must be cleared by writing '1'.

| 7        | 6        | 5        | 4       | 3       | 2    | 1      | 0   |

|----------|----------|----------|---------|---------|------|--------|-----|

| Reserved | Reserved | Reserved | SEND_OK | TIMEOUT | RECV | DISCON | CON |

| Bit | Symbol   | Description                                                              |

|-----|----------|--------------------------------------------------------------------------|

| 7   | Reserved | Reserved                                                                 |

| 6   | Reserved | Reserved                                                                 |

| 5   | Reserved | Reserved                                                                 |

| 4   | SEND_OK  | It is set as '1' if send operation is completed.                         |

| 3   | TIMEOUT  | It is set as '1' if Timeout occurs during connection establishment or    |

|     |          | termination and data transmission.                                       |

| 2   | RECV     | It is set as '1' whenever W5100 receives data. And it is also set as '1' |

|   |        | if received data remains after execute CMD_RECV command.             |

|---|--------|----------------------------------------------------------------------|

| 1 | DISCON | It is set as '1' if connection termination is requested or finished. |

| 0 | CON    | It is set as '1' if connection is established.                       |

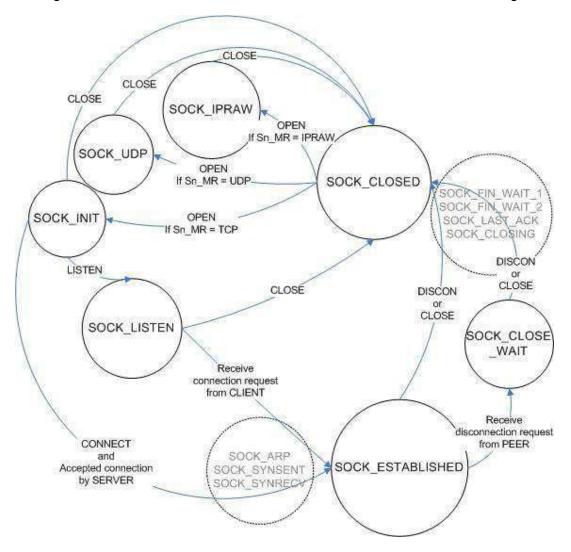

#### Sn\_SR (Socket n Status Register) [R] [0x0403, 0x0503, 0x0603, 0x0703] [0x00]

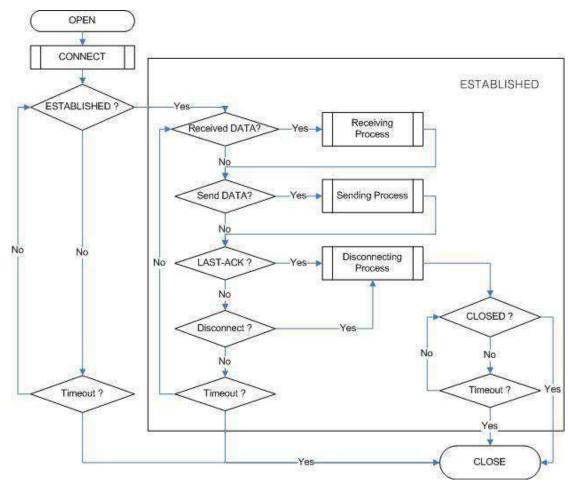

This register has the status value of socket n. The main status is shown in the below diagram.

| Value | Symbol      | Description                                               |

|-------|-------------|-----------------------------------------------------------|

| 0x00  | SOCK_CLOSED | It is shown in case that CLOSE commands are given to      |

|       |             | Sn_CR, and Timeout interrupt is asserted or connection is |

|       |             | terminated. In this SOCK_CLOSED status, no operation      |

|       |             | occurs and all resources for the connection is released.  |

| Ox13 SOCK_INIT  It is shown in case that Sn_MR is set as TCP and commands are given to Sn_CR. This is the initial status, the command type (LISTEN or CONNECT) of will decide the operation type - TCP server mode or mode.  Ox14 SOCK_LISTEN  It is shown in case that LISTEN commands are given the Sock_INIT status. The related socked operate as TCP Server mode, and become ESTBLISHED if connection request is normally received.  Ox17 SOCK_ESTABLISHED  It is shown in case that connection is established. It is shown in case that connection termination requests. | ep for K_INIT Sn_CR Client en to t will |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Sn_CR at the SOCK_INIT status. The related socked operate as TCP Server mode, and become ESTBLISHED if connection request is normally received.  Ox17 SOCK_ESTABLISHED It is shown in case that connection is established. It is status, TCP data is transmitted and received.                                                                                                                                                                                                                                                                                                 | t will                                  |

| status, TCP data is transmitted and received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |

| 0x1C SOCK_CLOSE_WAIT It is shown in case that connection termination requ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | n this                                  |

| received from peer host. At this status, the Acknown message has been received from the peer, but disconnected. The connection can be closed by received by the DICON or CLOSE commands.                                                                                                                                                                                                                                                                                                                                                                                       | /ledge<br>t not                         |

| Ox22 SOCK_UDP  It is shown in case that OPEN commands are given to when Sn_MR is set as UDP. As this status does not need connection process with peer, the data can be distransmitted and received.                                                                                                                                                                                                                                                                                                                                                                           | ed the                                  |

| Ox32 SOCK_IPRAW  It is shown in case that OPEN commands are given to when Sn_MR is set as IPRAW. At the IPRAW status following protocols of IP Header are not processed. Ref"  "IP RAW" for more information.                                                                                                                                                                                                                                                                                                                                                                  | s, the                                  |

| Ox42 SOCK_MACRAW  It is shown in case that OPEN commands are given to when SO_MR is set as MACRAW.  At the MAC RAW status, there is no protocol process packet. For more information, refer to "MAC RAW".                                                                                                                                                                                                                                                                                                                                                                      |                                         |

| 0x5F SOCK_PPPOE It is shown in case that OPEN commands are given to when SO_MR is set as PPPoE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

#### Below is shown during changing the status.

| Value | Symbol       | Description                                                               |

|-------|--------------|---------------------------------------------------------------------------|

| 0x15  | SOCK_SYNSENT | It is shown in case that CONNECT commands are given to                    |

|       |              | Socket <i>n</i> Command Register(S <i>n</i> _CR) at the SOCK_INIT status. |

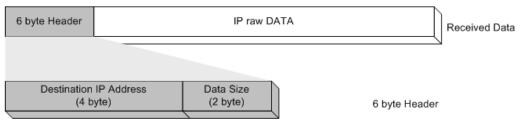

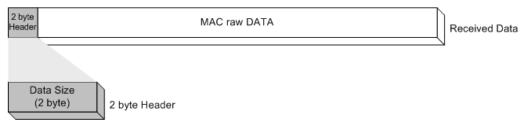

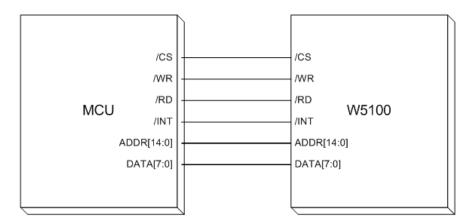

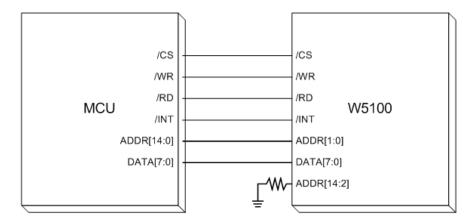

|       |              | It is automatically changed to SOCK_ESTABLISH when the                    |